# 数字压电叠堆执行器:原理、建模与控制

凌杰\* 张允执 陈龙 朱玉川

南京航空航天大学机电学院,南京,210016

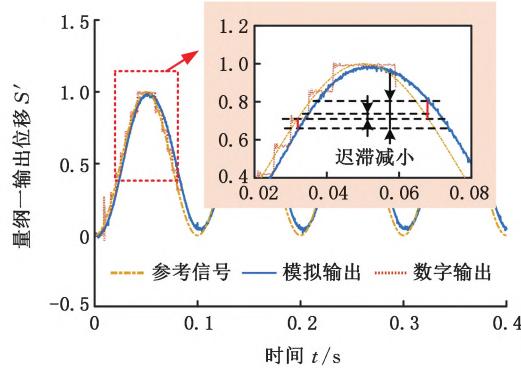

**摘要:**针对高精度驱动需求,从新型离散构型和数字驱动原理出发,首先探究不同数字编码方式下数字压电叠堆执行器的动、静态输出特性;其次探究数字驱动下迟滞减小的内在机理,结合非线性动力学数学建模描述执行器的迟滞、蠕变和动力学等特性;最后提出数字开/关时间控制来消除剩余迟滞,进一步提高定位精度。实验结果表明,相比传统压电叠堆,数字压电叠堆迟滞减小66%以上,所提的建模方法在10 Hz以内均方根误差小于0.3889 μm,所提的数字开/关时间控制方法能够在10 Hz以内有效消除执行器剩余迟滞特性的影响。

**关键词:**智能材料;驱动技术;迟滞;数字控制

**中图分类号:**TH7;TP223

DOI:10.3969/j.issn.1004-132X.2025.02.005

**开放科学(资源服务)标识码(OSID):**

## Digital Piezoelectric Stack Actuators: Principle, Modeling and Control

LING Jie\* ZHANG Yunzhi CHEN Long ZHU Yuchuan

College of Mechanical and Electrical Engineering, Nanjing University of Aeronautics and

Astronautics, Nanjing, 210016

**Abstract:** Based on the new discrete configuration and the principle of digital drive, the dynamic and static output characteristics of a digital piezoelectric stack actuator(DPEA) were studied under different digital coding modes. Secondly the internal mechanism of hysteresis reduction under digital drive, was explored, and described the hysteresis, creep and dynamics characteristics of the DPEA were combined with nonlinear dynamic mathematical modeling. Finally, digital on/off time control was proposed to eliminate the remaining hysteresis and further improve the positioning accuracy. Experimental results show that compared to traditional piezoelectric stacks, the hysteresis of DPEA is reduced by more than 66%. The proposed modeling method yields a root mean square error of less than 0.3889 μm within 10 Hz. The proposed digital on/off time control may effectively eliminate the residual hysteresis of the DPEA within 10 Hz.

**Key words:** smart material; driving technology; hysteresis; digital control

### 0 引言

压电材料作为一种能直接实现电-机转换的智能材料<sup>[1]</sup>,因高分辨率、高能量密度、高频响和结构紧凑的优势而成为精密运动系统中的重要驱动元件,广泛运用于微/纳操作、航空航天驱动系统、半导体加工等领域<sup>[2-3]</sup>。由于单片压电陶瓷的输出位移较小,实际使用中常通过粘接工艺将多片压电陶瓷片和电极叠合,形成压电叠堆以放大位移<sup>[4]</sup>。但是,压电材料固有的迟滞非线性会引起其输出精度的降低和闭环系统的振荡<sup>[5-6]</sup>,限制了其在快速、高精密定位系统中的应用。

目前已有三种方法可用于抑制或消除迟滞非线性。第一种方法是通过设计控制器补偿迟滞,其中包括:<sup>①</sup>无迟滞模型的控制<sup>[7]</sup>;<sup>②</sup>有迟滞模型的控制<sup>[8]</sup>。前者因为反馈控制带宽太低,无法

解决高频、大位移下的迟滞非线性,同时,也面临控制稳定性和性能提升的矛盾,控制器的设计往往十分复杂。后者采用构建迟滞模型的方式,在此基础上构建前馈控制器以消除迟滞。考虑到未建模误差导致的控制器失效问题<sup>[9-10]</sup>,目前常用前馈-反馈复合控制的方式补偿未建模误差,其难点在于考虑逆补偿误差时的闭环稳定性问题。第二种方法是采用电荷控制的方式消除迟滞。但由于电荷放大器研制复杂、成本高昂,故电荷控制方法目前并未被广泛应用<sup>[11]</sup>。第三种抑制迟滞的方法是结合离散和数字编码的思想,利用数字信号对各离散压电层进行逐层驱动,实现迟滞的减小。实现这种驱动方式需要进行以下工作:<sup>①</sup>在机械连接上将传统压电叠堆离散为多层结构、互相叠加但不粘接;<sup>②</sup>在电气驱动上,每一层都有一对独立的正负端子用以驱动,而不是各压电层共享一对驱动电极,以此释放控制自由度;<sup>③</sup>在

收稿日期:2024-03-07

基金项目:航空科学基金(ASFC-20220007052001)

控制原理上,对离散后的多层压电叠堆按层进行编码,利用一系列方波数字信号对各离散压电层进行开/关控制,实现从“单自由度模拟控制”向“多自由度数字控制”的转变。这种离散数字驱动的数字压电执行器最早由 XIA 等<sup>[12]</sup>提出,通过 8 层厚度按二进制编码的离散压电叠堆组成,可以实现 256 位的位移输出,实验证明,该数字压电执行器的位移近似线性、平滑的输出。XIAO 等<sup>[13]</sup>利用相同原理实现了一种二进制编码下的数字压电双晶片执行器,实现了迟滞的减小。高强等<sup>[14]</sup>同样提出了一种离散结构和二进制编码的阵列压电叠堆执行器,通过仿真验证了其工作原理。可见,第三种方法无需设计复杂的闭环控制器和昂贵的电荷放大器,通过离散和数字编码的数字信号驱动即可实现减小迟滞。目前国内外关于数字压电执行器的研究存在以下不足:①在驱动原理方面,并没有对数字驱动下减小迟滞的原理进行解释;②在理论建模方面,目前文献中并没有对数字驱动下的压电执行器非线性动力学进行建模;③数字压电执行器的迟滞虽然有所减小,但依然存在剩余迟滞,设计相关控制方法对剩余迟滞进行消除的研究目前未见报道。

本文针对数字压电叠堆执行器,较完整地完成了以下工作:①从不同数字编码的角度对执行器的静态、动态特性进行分析;②将数字/传统压电执行器的迟滞非线性进行比较,并完成数字驱动下迟滞减小的原理分析;③完成了执行器非线性动力学建模;④针对数字驱动下剩余迟滞非线性,提出了一种对应的数字开/关时间控制方法,进一步提高数字压电叠堆执行器的输出精度。

## 1 数字压电叠堆执行器结构和原理

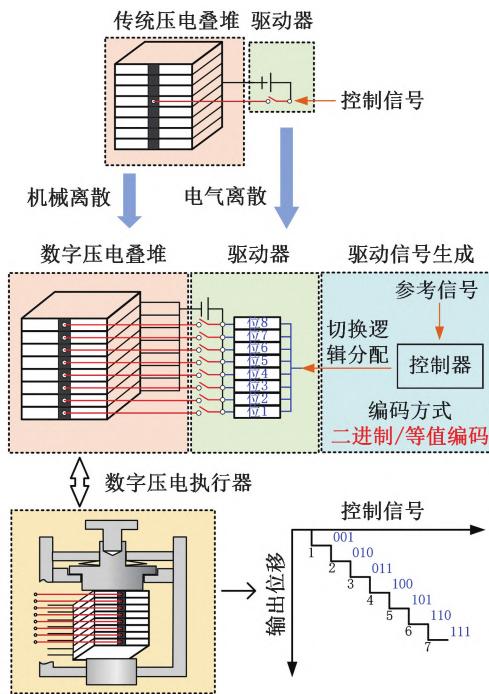

### 1.1 数字压电叠堆执行器结构设计

如图 1 所示,设计的数字压电叠堆执行器采用直驱式结构。直驱式结构相对于杠杆式、柔性放大式结构具有带宽高、结构简单、易于设计实现的优势。执行器中包含 8 层 10 mm×10 mm 的压电片,层与层之间在结构和驱动上都进行了离散,总计释放 8 对控制端口。

### 1.2 数字压电叠堆执行器工作原理

数字压电叠堆执行器工作原理如图 1 所示。该系统由以下部分组成:8 层离散数字压电叠堆、驱动器和控制器。其中,控制器进行数据采集、处理和控制信号的生成、输出;驱动器有 8 对输入-输出的功率放大驱动电路,其功能是将 0~5 V 指令方波信号转换为 0~100 V 的驱动信号;数字压

图 1 数字压电叠堆执行器结构与工作原理

Fig.1 Structure and working principle of DPEA

电叠堆执行器作为核心驱动单元,最终输出位移。与传统压电叠堆往往通过模拟谐波信号进行控制不同的是,数字压电叠堆各层控制信号为一系列独立的方波。为了实现“类模拟谐波驱动”的输出位移,需要对原本的模拟信号按压电层数进行比例放大,即

$$U = 2.5n_p \sin(\omega t + 1.5\pi) + 2.5n_p \quad (1)$$

式中: $U$  为按压电层数放大后的电压信号; $n_p$  为压电层数; $\omega$  为信号角频率。

此处  $2.5n_p$  为直流偏置,防止压电承受负压而击穿。

再按压电层数进行数字量化:

$$U_q = \frac{U_{\max}}{n_p} \text{round}\left(\frac{U}{U_{\max}}\right) \quad (2)$$

式中: $U_q$  为量化后信号; $\text{round}()$  为四舍五入取整函数。

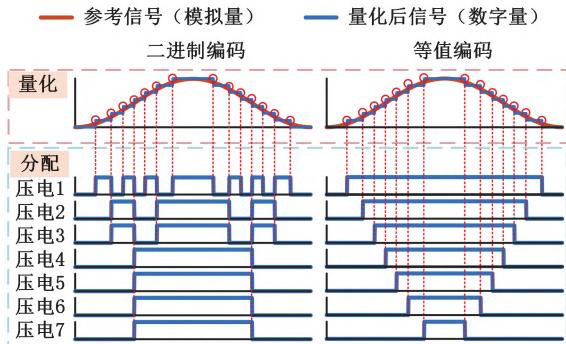

根据量化后信号进行各压电层驱动信号的分配:由于控制器数字输出只能输出 5 V 的高电平和 0 V 低电平,故每一层压电的驱动信号幅值为 5 V;各层开/关时间由编码方式决定。本文着重讨论最常见的编码方法:二进制编码和等值编码下,数字压电叠堆的静态、动态输出特性。由于只有 8 层压电,二进制数最多为 [1 1 1],故实际工作时,只有 7 层压电被驱动。两种编码下各压电层开/关切换方法如图 2 所示:①对于二进制编码的 7 层数字压电,可按二进制数 001、010、100,分别设置第一层压电为 001,第二、三层压电为 010,第四~七层压电为 100;②对于等值编码,则每层压电均为 1。量化后信号的每一级输出位移与编

码数一一对应,实际工作时根据所需位移即可确定编码数,以此确定各层压电的实时开/关切换状态。

图2 数字压电叠堆执行器信号切换逻辑分配

Fig.2 Signal switching logic distribution of DPEA

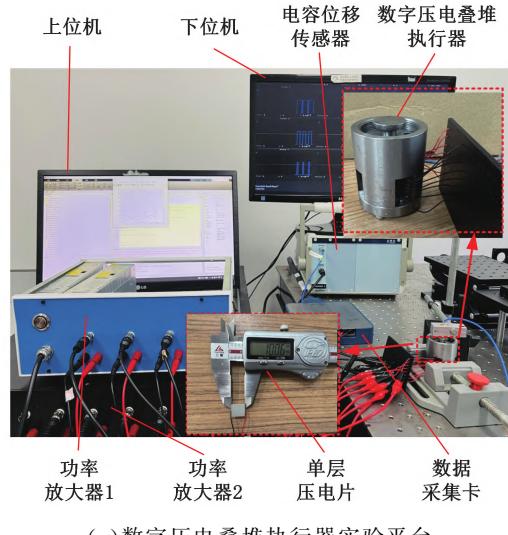

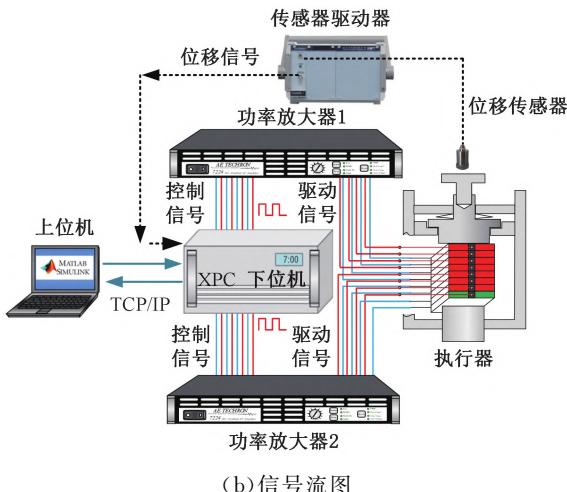

### 1.3 数字压电叠堆执行器实验平台

数字压电叠堆执行器实验平台与信号流图见图3。基于xPC-Target实时控制系统,由运动采集卡(NI公司,PCI-6259)、上位机和下位机等组成。

(a)数字压电叠堆执行器实验平台

图3 实验平台与信号流图

Fig.3 Experimental platform and the signal flow

成。上位机指令经由7组独立输入-输出口的功率放大器驱动7层数字压电叠堆(哈尔滨芯明天公司,NAC2015),电容位移传感器(哈尔滨芯明天公司,E09.Cap)反馈到下位机采集卡并由局域网上传至上位机。

## 2 数字压电叠堆执行器静态、动态输出特性分析与实验

针对常用的二进制编码和等值编码方式,分析不同驱动方式下数字压电叠堆执行器的静态、动态输出特性。

### 2.1 数字压电叠堆执行器静态输出特性分析

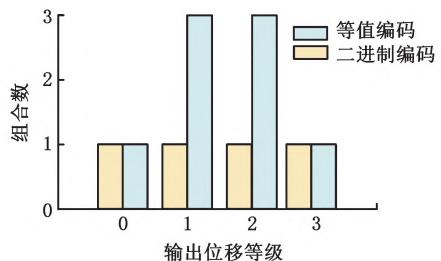

静态输出特性是指数字压电叠堆执行器在不同编码方式下实现相同位移的组合数,直接反映了执行器的性能冗余性和容错能力。对于二进制编码,每一种输出位移对应的驱动压电组合是唯一的;而对于等值编码,非满量程输出位移的组合数不唯一。以三层数字压电叠堆为例,不同输出位移等级下等值编码与二进制编码的组合数比较如图4所示。相比二进制编码,等值编码的输出位移组合数冗余性更强:当数字压电叠堆的层数相同时,在相同的输出位移等级下,等值编码具备的组合数大于或等于二进制编码的组合数,即等值编码的容错能力更强。

图4 不同输出位移等级下等值编码与二进制编码的组合数比较

Fig.4 Comparison of combination numbers of equivalent/binary coding under different displacement levels

### 2.2 数字压电叠堆执行器动态输出特性分析

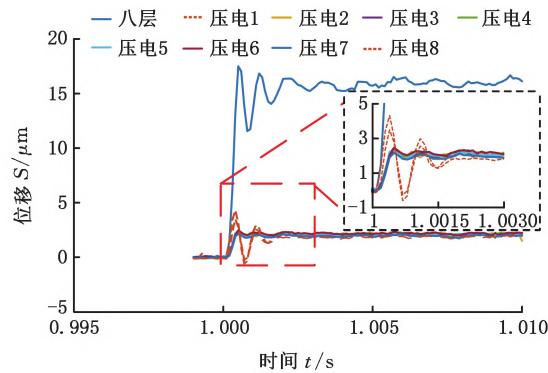

动态输出特性指执行器从一个输出位移状态向另一个状态改变时的瞬态输出特性,能够体现执行器的切换稳定性。数字压电叠堆执行器的动态输出特性取决于每层压电响应特性差异。图5所示为八层同时驱动和各层独立驱动下执行器整体的阶跃响应。可以明显看出,执行器的阶跃响应都近似于一个欠阻尼系统。此外,两端的压电层阶跃响应有别于中间层的阶跃响应,体现为响应速度更快,超调量更大。这种响应差异性最终会体现为状态切换时的瞬态输出特性。

图 5 数字压电叠堆执行器阶跃响应

Fig.5 Step response of DPEA

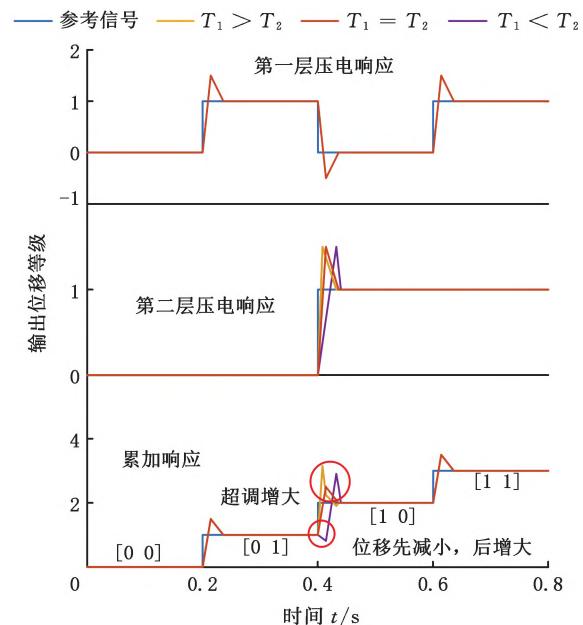

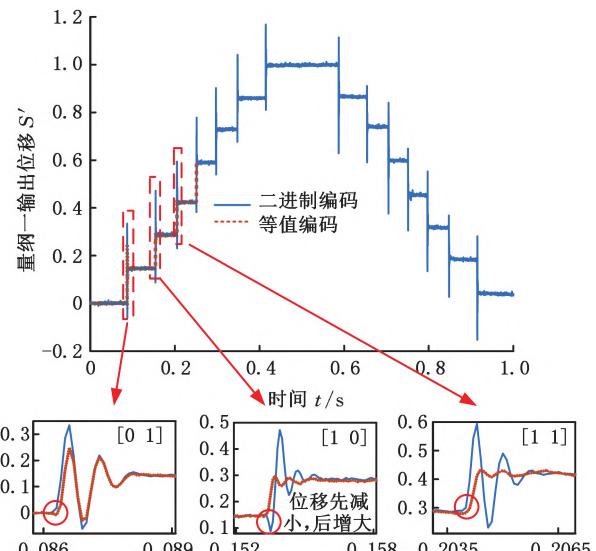

通过阶跃响应实验辨识出每层压电层的传递函数,通过仿真得到两种编码方式下数字压电叠堆执行器的动态特性,如图 6 所示。可见:①针对两种编码方式,数字压电叠堆的第一层压电被驱动时,两种编码动态特性相同;②等值编码下压电层逐层驱动后再逐层关闭,除第一层输出位移的超调明显以外,其余各层在打开和关闭时超调均不明显。与之相对,由于二进制编码下,输出位移等级在切换时对应的二进制数为 001 的第一层压电层的开闭状态总是会随之切换,故每一级输出的位移都会因第一层压电状态切换的关系而具有明显的超调。

图 6 两种编码方式下数字压电叠堆的动态特性

Fig.6 Dynamic characteristics of the DPEA under two encoding methods

为研究层间响应特性差异对瞬态输出特性的影响,在仿真中以两层压电为例。设第一层压电的输出位移等级为 1,响应时间为  $T_1$ ,第二层压电的输出位移等级为 2,响应时间为  $T_2$ ,按二进制编码。仿真设置第二层压电的响应时间  $T_2$  分别小于  $T_1$ 、等于  $T_1$  和大于  $T_1$ ,得到二进制编码下的执行器位移输出特性如图 7 所示。可见,对于二进制编码:①当所需输出位移等级为奇数时,数字压电叠堆的动态特性几乎由第一层的动态特性决定;②当所需输出位移等级为偶数时,若  $T_2 \neq T_1$ ,执行器的输出位移会产生突变。具体表

现为位移超调量变大或位移先减小再增大的现象。另外,当所有压电层的工作状态都发生变化,即编码从  $[0\ 1]$  切换为  $[1\ 0]$  时,位移突变最明显。

图 7 二进制编码层间响应差异与输出位移关系

Fig.7 Response difference and displacement output relationship between binary coding layers

### 2.3 数字压电叠堆执行器开环实验

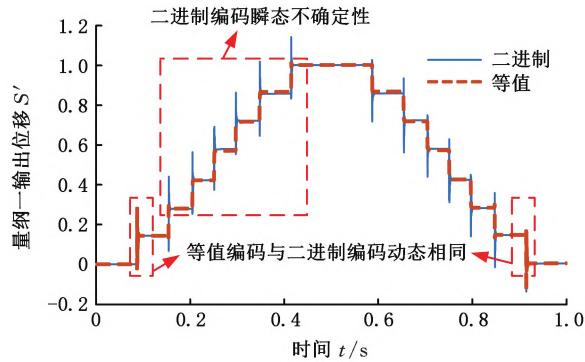

为了验证数字压电叠堆执行器驱动原理和动态输出性能分析的准确性,进行数字压电叠堆执行器开环实验。实验测得两种编码下的输出位移结果如图 8 所示。可见,实验结果与分析结果基本一致,位移从  $[0\ 1]$  切换为  $[1\ 0]$  时出现了先减小再增大的情况,而超调量的变化并不明显。

综上,由于压电层间差异性的原因,不同压电

图 8 两种编码下层间响应差异与输出位移关系

实验结果

Fig.8 Experimental results of relation between response difference and displacement output under two coding mode

层的动态响应时间和超调量必然存在一定程度上的差异。相比于二进制编码,等值编码由于在切换过程中有且仅有一层的运动状态会发生改变,其输出位移的瞬态不确定性较小、位移突变较小,有助于提高数字压电叠堆执行器的稳定性与控制精度。对于二进制编码,后续也可采用阻尼控制的方式减小各层响应差异和位移突变。

### 3 数字压电叠堆执行器迟滞非线性特性分析与实验

迟滞非线性作为压电的固有特性,在模拟信号驱动时体现为输入电压与输出位移的非线性与多值映射关系。压电内部不完全可逆的非180°畴的转向是迟滞产生的原因<sup>[15]</sup>。场强  $E$  与180°畴转向的晶胞数  $m$  的关系为

$$m(E \uparrow) < m(E \downarrow) \quad (3)$$

场强越大,非180°畴转向的晶胞数  $m$  越多,压电的迟滞越严重。但相同幅值、不同类型的驱动信号也会影响压电的迟滞。

#### 3.1 数字压电叠堆执行器迟滞特性分析

对模拟整体式模拟驱动和数字驱动下的迟滞进行比较,解释数字压电叠堆执行器迟滞减小的原因。

首先需要确定其一个驱动周期内的电场强度。针对模拟驱动,模拟驱动信号  $U_a$  为

$$U_a = \frac{A}{2} \sin(\omega t + 1.5\pi) + \frac{A}{2} \quad (4)$$

式中: $A$  为信号峰峰值。

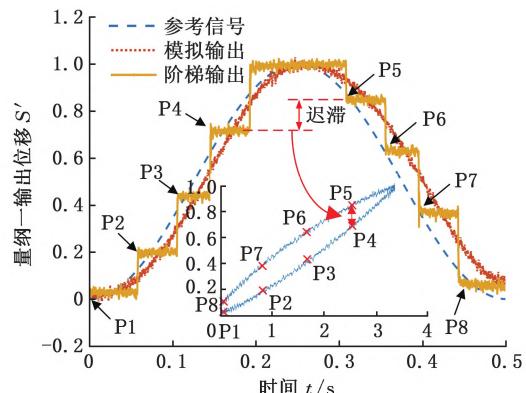

正弦驱动信号下的执行器输出位移及滞环如图9所示,为了方便观察迟滞变化,将各个信号都进行了归一化处理。可以看到,正弦驱动下的滞环两边小、中间大。对于模拟驱动,信号幅值越接近峰值或者谷值,迟滞越小。采用相同峰-峰值的阶梯信号近似代替模拟驱动信号时,每一级阶梯所对应的位移在滞环上是离散的点,可见在相同

图9 单层压电不同驱动信号下的输出位移迟滞特性

Fig.9 Hysteresis characteristics of single layer piezoelectric with different driving signals

输入电压下,迟滞并没有减少。但当阶梯只有一级,即压电以方波进行驱动时,迟滞只出现在图9中的P1和P8处,该处的迟滞很小。因此,在数字驱动下,由于信号只是方波信号,每一层压电被驱动时,其迟滞只包含图9中P8处的迟滞,相对于等幅值的模拟信号驱动时很小。

#### 3.2 数字压电叠堆执行器迟滞特性实验

为了验证数字压电叠堆执行器在数字驱动下的迟滞比模拟驱动下更小的优势,分别对7层数字压电叠堆执行器进行模拟驱动和数字驱动。

模拟式和数字式驱动的输入信号幅值相同、频率相同。实验依次在三种驱动频率1、5、10 Hz下,比较数字压电叠堆执行器在不同驱动信号下的迟滞大小,实验结果如图10所示。可见,对于

(a) 驱动频率 1 Hz

(b) 驱动频率 5 Hz

(c) 驱动频率 10 Hz

图10 不同驱动信号下的数字压电叠堆执行器输出位移

Fig.10 Output displacement of DPEA under different driving signals

同一电压幅值,数字驱动相较于模拟驱动的迟滞大大减小,并且数字驱动下的输出位移与参考信号之间基本不存在滞后。

进一步量化不同驱动方式下迟滞的减小,分别在驱动频率1、5、10 Hz下,比较在同一电势下的迟滞大小,见表1~表3。相比于传统整体式模拟驱动,数字驱动下的迟滞平均减小69.24%(1 Hz),66.97%(5 Hz),68.57%(10 Hz),且当驱动信号为10 Hz时,迟滞最大可减小83.33%。

表1 驱动频率1 Hz下不同驱动方式的迟滞对比

Tab.1 Hysteresis comparison of different driving modes under 1 Hz

| 序号 | 电势/V | 模拟迟滞/ $\mu\text{m}$ | 数字迟滞/ $\mu\text{m}$ | 迟滞减幅/% |

|----|------|---------------------|---------------------|--------|

| 1  | 0    | 0.696               | 0.509               | 26.85  |

| 2  | 10   | 2.450               | 0.613               | 75.00  |

| 3  | 20   | 2.340               | 0.438               | 81.27  |

| 4  | 30   | 1.199               | 0.264               | 77.96  |

表2 驱动频率5 Hz下不同驱动方式的迟滞对比

Tab.2 Hysteresis comparison of different driving modes under 5 Hz

| 序号 | 电势/V | 模拟迟滞/ $\mu\text{m}$ | 数字迟滞/ $\mu\text{m}$ | 迟滞减幅/% |

|----|------|---------------------|---------------------|--------|

| 1  | 0    | 0.651               | 0.632               | 2.97   |

| 2  | 10   | 2.640               | 0.651               | 75.37  |

| 3  | 20   | 2.605               | 0.477               | 81.68  |

| 4  | 30   | 1.257               | 0.264               | 78.97  |

表3 驱动频率10 Hz下不同驱动方式的迟滞对比

Tab.3 Hysteresis comparison of different driving modes under 10 Hz

| 序号 | 电势/V | 模拟迟滞/ $\mu\text{m}$ | 数字迟滞/ $\mu\text{m}$ | 迟滞减幅/% |

|----|------|---------------------|---------------------|--------|

| 1  | 0    | 0.677               | 0.574               | 6.67   |

| 2  | 10   | 2.759               | 0.522               | 76.40  |

| 3  | 20   | 2.585               | 0.464               | 81.55  |

| 4  | 30   | 1.586               | 0.264               | 83.33  |

## 4 数字压电叠堆执行器建模与实验

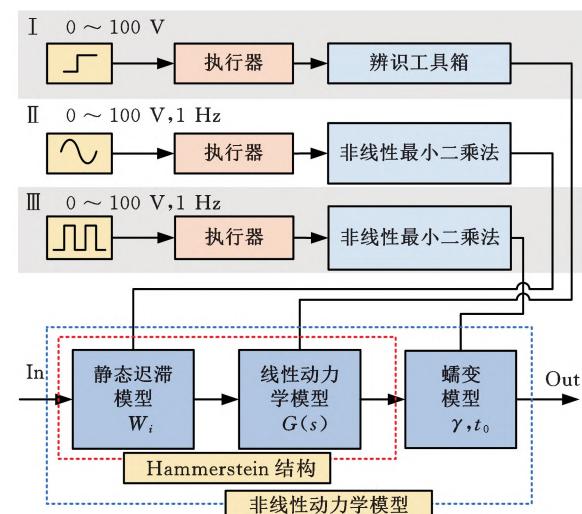

### 4.1 数字压电叠堆执行器非线性动力学建模

由于压电本身具有固有的迟滞非线性和蠕变非线性,故在建立执行器动力学模型时需要同时引入迟滞模型和蠕变模型。

对于迟滞非线性,由于数字压电叠堆执行器的迟滞只关心压电在方波低电平下的迟滞,故迟滞远小于模拟式的驱动。但是,由于迟滞依然存在,为了建立准确的数字压电叠堆执行器非线性动力学模型,仍然需要考虑迟滞非线性。Hammerstein结构作为一种模拟率相关迟滞非线性的迟滞模型<sup>[16]</sup>,由静态迟滞模型和线性动力学模型级联而成。考虑迟滞和线性动力学的数字压电叠堆执行器动力学模型可由Hammerstein的结构

实现。其中,静态迟滞模型采用Prandtl-Ishlinskii(P-I模型)<sup>[17]</sup>:

$$Y[u](t) = w_0 u(t) + \sum_{i=1}^n w_i Hr_i[u](t) \quad (5)$$

其中, $Y(u)$ 为模型输出; $w_i$ 为算子权重; $u$ 为输入信号; $r_i$ 为算子阈值; $i$ 为算子编号; $Hr_i(u)$ 为齿隙算子, $t_s$ 为采样时间。 $Hr_i(u)$ 表达式为

$$\begin{aligned} Hr_i[u](t) = \\ \max(u(t) - r_i, \min(u(t) + r_i, Hr_i[u](t - t_s))) \end{aligned} \quad (6)$$

数字压电叠堆执行器的线性动力学模型由阶跃响应直接辨识获得。压电的蠕变非线性是指当压电执行器被驱动时的输出位移漂移现象,在低速运行时,压电的蠕变非线性会变得很明显<sup>[18]</sup>。因此,当压电驱动器接受方波信号时,在瞬态响应后的几毫秒后会产生明显蠕变的特点,直到下一个电平变化的时刻。在Hammerstein结构的基础上,需要考虑蠕变模型。蠕变模型采用对数函数的形式描述<sup>[19]</sup>。同时,蠕变在方波信号的上升沿和下降沿发生后都会出现,原本的蠕变模型只适用于上升沿,对蠕变模型进行改进:

$$L(t) = \begin{cases} 1 + \gamma \lg \frac{tf}{n-1+t_0} & \text{上升沿蠕变} \\ 1 - \gamma \lg \frac{tf}{n-1+t_0-t_b} & \text{下降沿蠕变} \end{cases} \quad (7)$$

式中: $L$ 为模型输出; $L_0$ 为蠕变开始时的位移; $\gamma$ 为蠕变因子; $t_b$ 为1 Hz下每个驱动周期中每一层压电的启动时刻; $t_0$ 为每个驱动周期中动态响应至蠕变开始的时间; $t$ 为当前时间; $n$ 为当前驱动的周期数; $f$ 为驱动频率。

蠕变模型中的参数 $\gamma$ 和 $t_0$ 由对数字压电叠堆执行器数字驱动实验的开环数据进行辨识得到。考虑迟滞、蠕变和线性动力学的数字压电叠堆执行器动力学模型如图11所示。

图11 非线性动力学模型辨识流程

Fig.11 Identification of the nonlinear dynamic model

## 4.2 数字压电叠堆执行器动力学模型参数辨识

首先通过阶跃响应实验辨识各层压电的线性动力学模型。该模型忽略迟滞和蠕变的非线性行为,只考虑线性部分。得到线性动力学模型后,通过准静态正弦信号驱动压电执行器的实验数据辨识静态 P-I 模型的参数。在正弦激励下,蠕变可忽略,因此可以得到忽略蠕变的动力学模型。最后通过方波信号驱动执行器获得的输出位移数据,在建立的 Hammerstein 结构基础上辨识蠕变模型参数,获得考虑蠕变的执行器非线性动力学模型。

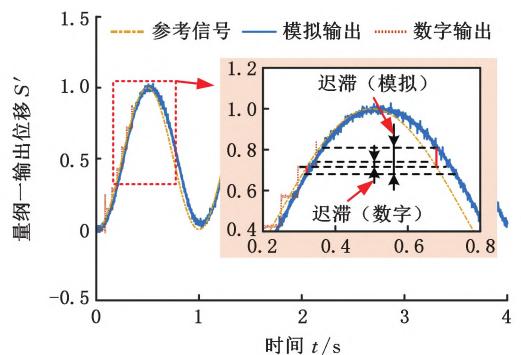

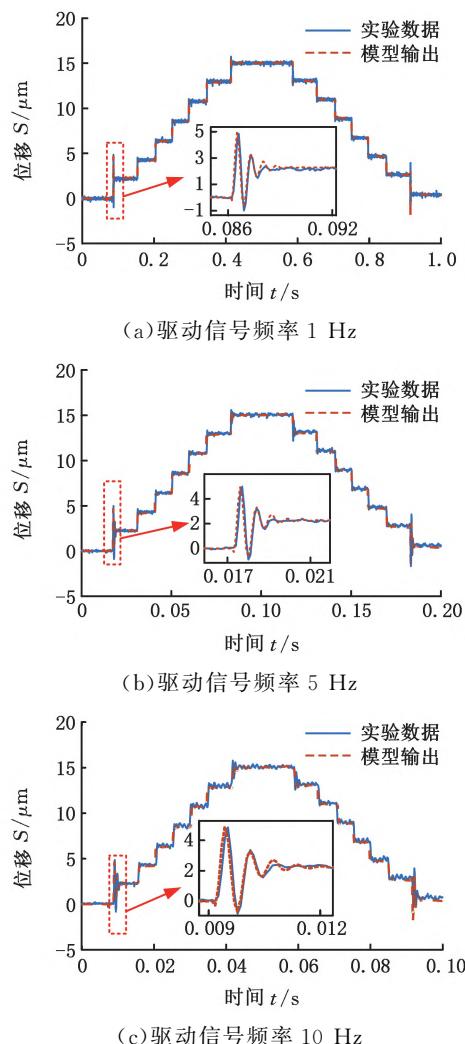

## 4.3 数字压电叠堆执行器非线性动力学模型验证

将辨识所得模型与数字驱动下的输出位移实验数据进行比较,结果如图 12 所示。可见,数字压电叠堆动力学模型可以较好地模拟数字压电叠堆执行器的动力学、迟滞和蠕变。为进一步验证模型的有效性,计算不同频率下的模型均方根误差。经过误差计算,建立的数字压电叠堆动力学

图 12 数字压电叠堆执行器动力学模型验证

Fig.12 Verification of the dynamic model of DPEA

模型在 1、5、10 Hz 下的均方根误差分别为 0.1279、0.2754、0.3889  $\mu\text{m}$ 。由此可见,本文建立的数字压电执行器动力学模型在 10 Hz 下具有较高的准确性。

## 5 数字压电叠堆执行器控制

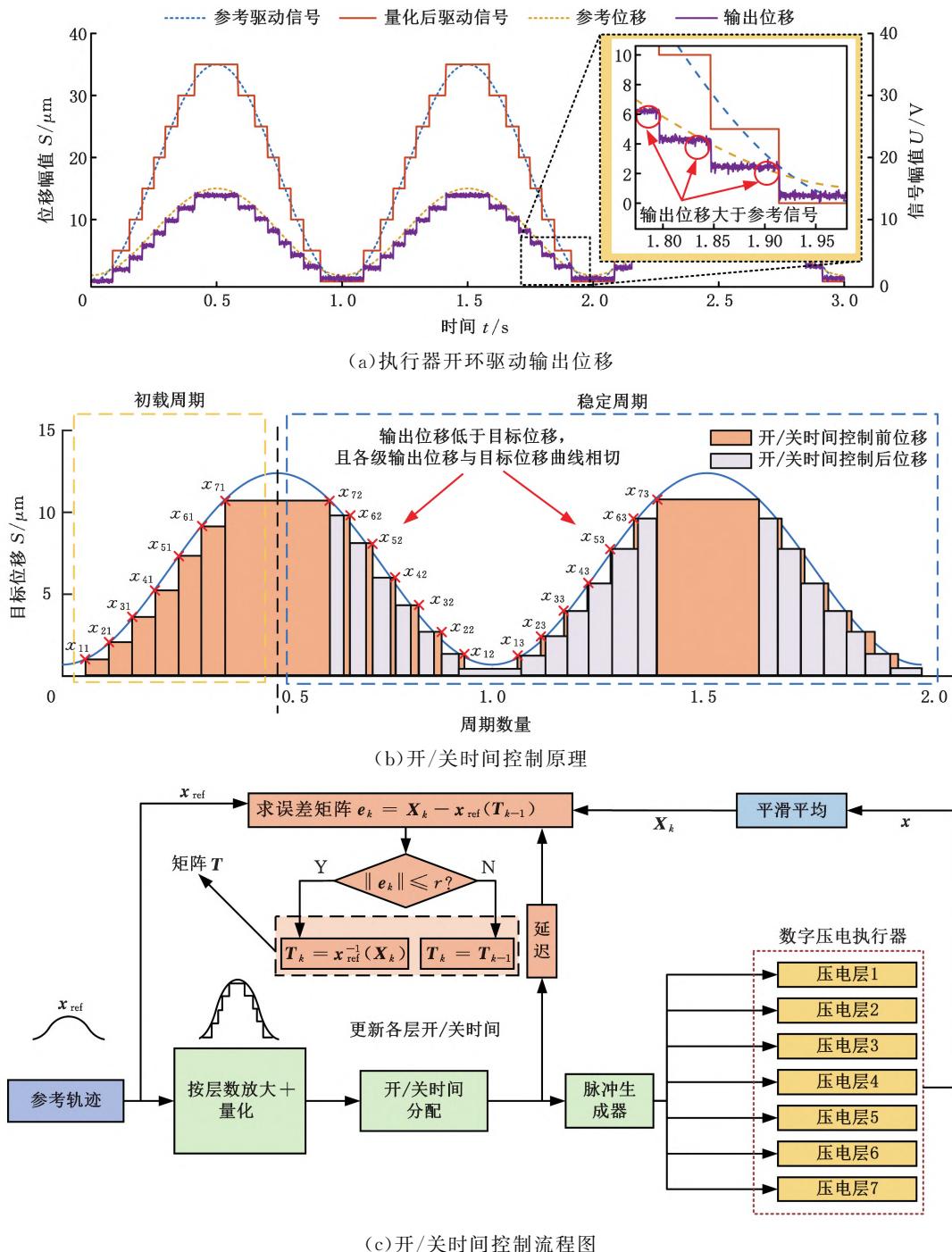

### 5.1 数字压电叠堆执行器数字开/关时间控制设计

数字压电叠堆执行器由于各层压电存在迟滞非线性,实际输出位移往往会在输入电压下降时大于参考位移信号,造成定位误差,如图 13a 所示。因此,需要根据执行器的实际输出位移进行各层开/关时间的控制,目的是确保整体的输出位移低于参考位移且各级输出位移与参考位移曲线相切,达到实际输出位移的“严格类谐波输出”,如图 13b 所示。

本文所采取的数字开/关时间控制方法是基于各层压电层实际输出位移进行开/关时间的修正,其控制流程如图 13c 所示。压电材料本身的输出位移在初载周期和稳定周期是不同的,设数字压电叠堆执行器的输出位移矩阵为

$$\mathbf{X} = \begin{bmatrix} x_{11} & x_{12} & x_{13} \\ x_{21} & x_{22} & x_{23} \\ \vdots & \vdots & \vdots \\ x_{i1} & x_{i2} & x_{i3} \end{bmatrix} \quad (8)$$

其中, $i=1,2,\dots,N$ , $N$  为压电总个数。 $\mathbf{X}$  是一个  $7 \times 3$  矩阵(总计 7 层压电被驱动),每一行为第  $i$  层压电层的输出位移信息,第一列元素  $x_{i1}$  代表第  $i$  层压电层在初载周期打开时的输出位移;第二列元素  $x_{i2}$  代表第  $i$  层压电层在稳定周期关闭时的输出位移;第三列元素  $x_{i3}$  代表第  $i$  层压电层在稳定周期打开时的输出位移,如图 13b 所示。

根据参考位移的反函数  $\mathbf{x}_{\text{ref}}^{-1}$  与输出位移矩阵  $\mathbf{X}$ ,得到数字压电叠堆执行器各层的开/关时间矩阵  $\mathbf{T}$ 。此处反函数  $\mathbf{x}_{\text{ref}}^{-1} = [\mathbf{x}_{\text{ref1}}^{-1} \quad \mathbf{x}_{\text{ref2}}^{-1} \quad \mathbf{x}_{\text{ref3}}^{-1}]$ ,依次为初载周期、稳定周期信号下降段和稳定周期信号上升段的反函数。开/关时间矩阵为

$$\begin{aligned} \mathbf{T} = \mathbf{x}_{\text{ref}}^{-1}(\mathbf{X}) = & \begin{bmatrix} \mathbf{x}_{\text{ref1}}^{-1}(x_{11}) & \mathbf{x}_{\text{ref2}}^{-1}(x_{12}) & \mathbf{x}_{\text{ref3}}^{-1}(x_{13}) \\ \mathbf{x}_{\text{ref1}}^{-1}(x_{21}) & \mathbf{x}_{\text{ref2}}^{-1}(x_{22}) & \mathbf{x}_{\text{ref3}}^{-1}(x_{23}) \\ \vdots & \vdots & \vdots \\ \mathbf{x}_{\text{ref1}}^{-1}(x_{i1}) & \mathbf{x}_{\text{ref2}}^{-1}(x_{i2}) & \mathbf{x}_{\text{ref3}}^{-1}(x_{i3}) \end{bmatrix} = \\ & \begin{bmatrix} t_{11} & t_{12} & t_{13} \\ t_{21} & t_{22} & t_{23} \\ \vdots & \vdots & \vdots \\ t_{i1} & t_{i2} & t_{i3} \end{bmatrix} \end{aligned} \quad (9)$$

其中,  $\mathbf{T}$  也是一个  $7 \times 3$  矩阵,  $\mathbf{T}$  的每一行元素为第  $i$  层压电层的开 / 关时间信息。第一列元素  $t_{i1}$  为第  $i$  层压电层初载周期的开启时刻;第二列元素  $t_{i2}$  为第  $i$  层压电层稳定周期的关闭时刻;第三列元素  $t_{i3}$  为第  $i$  层压电层稳定周期的开启时刻。

开 / 关矩阵每次更新完都进行一次记录。每一个周期开始前都将输出位移矩阵  $\mathbf{X}$  与前一次开 / 关矩阵对应的参考位移函数  $x_{\text{ref}}(\mathbf{T}_{k-1})$  进行误差计算, 若误差大于设定阈值  $r$ , 则再次更新开 / 关时间矩阵  $\mathbf{T}$ , 反之则  $\mathbf{T}$  保持不变, 如图 13c 所示。

图 13 执行器数字开/关时间控制

Fig.13 Digital on/off time control of DPEA

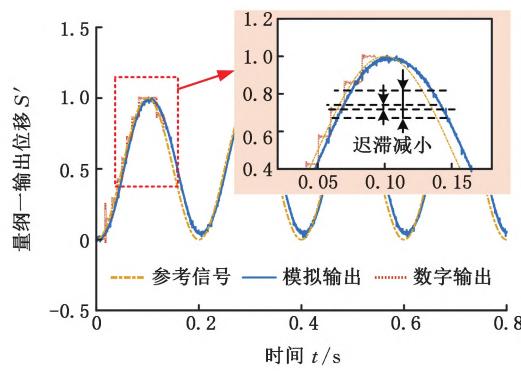

## 5.2 数字压电叠堆执行器数字开/关时间控制实验验证

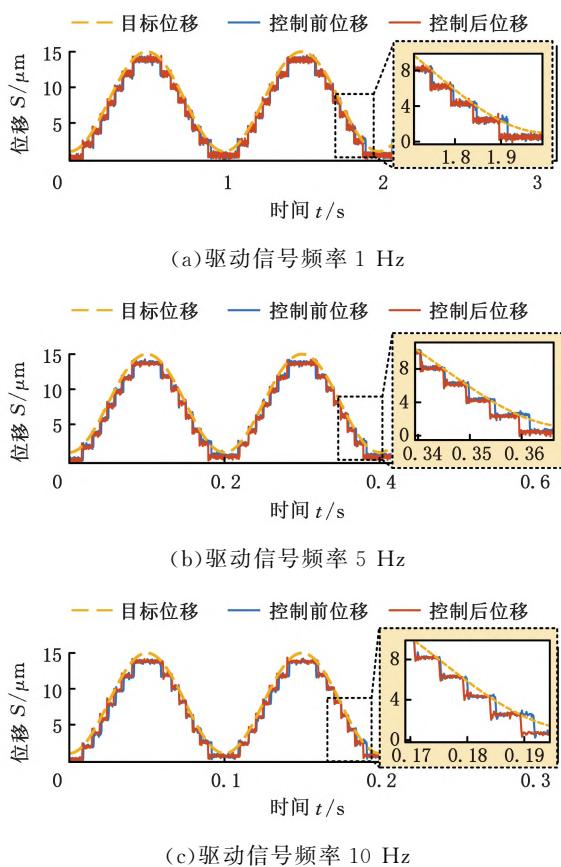

根据执行器数字开/关时间控制方法, 采用图 3 所示实验平台进行实验验证, 结果如图 14 所

示。可见, 当目标位移信号为 1、5、10 Hz 的正弦信号时, 相比于开/关时间控制前的输出位移, 开/关时间控制后的位移实现了控制目的, 即消除了层间迟滞非线性差异对输出位移的影响。

图 14 数字压电叠堆执行器开/关时间控制实验验证

Fig.14 Experimental verification of on/off time control of DPEA

## 6 结论

本文提出了一种新型数字压电叠堆执行器，并对其工作原理、驱动方式、建模理论和控制方法进行介绍，得出以下结论：

1)通过对数字压电叠堆执行器在不同编码方式下的静态、动态特性分析可得，相对于二进制编码，等值编码瞬态不确定性和位移突变较小，有助于提高数字压电叠堆执行器输出稳定性与精度。

2)通过对数字压电叠堆执行器在数字驱动下的迟滞非线性分析可得，相比于传统的整体式模拟驱动方式，数字驱动下的迟滞大幅减少，平均减小 69.24% (1 Hz), 66.97% (5 Hz), 68.57% (10 Hz)，且迟滞最多可减小 83.33%。

3)通过对数字压电叠堆执行器的动力学建模可得，考虑迟滞、线性动力学和蠕变因素后，所建模型精度较高，在 1、5、10 Hz 下的均方根误差(标准差)分别为 0.1279、0.2754、0.3889 μm。

4)考虑压电执行器迟滞非线性的影响，进行数字压电叠堆执行器数字开/关时间控制的设计与实验验证。实验结果证明开/关时间控制后：①

输出位移低于目标位移；②各级输出位移与目标位移曲线相切，即消除了层间迟滞非线性差异对输出位移的影响，实现了实际输出位移的“严格类谐波输出”。

## 参考文献：

- [1] JANOWICZ H, KUHNEN K. Real-time Compensation of Hysteresis and Creep in Piezoelectric Actuators[J]. Sensors and Actuators A: Physical, 2000, 79(2):83-89.

- [2] LING Jie, CHEN Long, FENG Zhao, et al. Development and Test of a High Speed Pusher-type Inchworm Piezoelectric Actuator with Asymmetric Driving and Clamping Configuration[J]. Mechanism and Machine Theory, 2022, 176:104997.

- [3] AN Dong, LI Ji, YANG Yixiao, et al. Compensation Method for Complex Hysteresis Characteristics on Piezoelectric Actuator Based on Separated Level-loop Prandtl-Ishlinskii Model[J]. Nonlinear Dynamics, 2022, 109(4):2479-2497.

- [4] 余学贵. 压电型步进式旋转精密驱动器试验研究[D]. 长春:吉林大学, 2005.

- [5] YU Xuegui. Design and Research on Precision Stepping Circumrotate Actuator Driving by Piezoelectricity[D]. Changchun:Jilin University, 2005.

- [6] HASSANI V, TJAHHOWIDODO T, DO T N. A Survey on Hysteresis Modeling, Identification and Control[J]. Mechanical Systems and Signal Processing, 2014, 49(1/2):209-233.

- [7] 魏燕定. 压电驱动器的非线性模型及其精密定位控制研究[J]. 中国机械工程, 2004, 15(7):565-568.

- [8] WEI Yanding. Study on Non-linear Model of Piezoelectric Actuator and Accurate Positioning Control Strategy[J]. China Mechanical Engineering, 2004, 15(7):565-568.

- [9] LING Jie, FENG Zhao, ZHENG Dongdong, et al. Robust Adaptive Motion Tracking of Piezoelectric Actuated Stages Using Online Neural-network-based Sliding Mode Control[J]. Mechanical Systems and Signal Processing, 2021, 150:107235.

- [10] MING Min, LING Jie, FENG Zhao, et al. A Model Prediction Control Design for Inverse Multiplicative Structure Based Feedforward Hysteresis Compensation of a Piezo Nanopositioning Stage[J]. International Journal of Precision Engineering and Manufacturing, 2018, 19(11):1699-1708.

- [11] 郝瑞, 彭倍, 周昊. 微机电系统压电振动台迟滞补偿方法研究[J]. 中国机械工程, 2021, 32(17): 2118-2124.

- [12] HAO Rui, PENG Bei, ZHOU Wu. Research on

- Hysteresis Compensation Method of MEMS Piezoelectric Vibratory Platforms [J]. China Mechanical Engineering, 2021, 32(17):2118-2124.

- [10] 胡斌梁, 陈国良. 压电陶瓷微夹钳迟滞环自适应逆控制研究[J]. 中国机械工程, 2006, 17(8):798-801.

- HU Binliang, CHEN Guoliang. Study on Adaptive Inverse Control of Hysteresis in Piezoelectric Microgripper [J]. China Mechanical Engineering, 2006, 17(8):798-801.

- [11] GU Guoying, ZHU Limin, SU Chunyi, et al. Modeling and Control of Piezo-actuated Nanopositioning Stages:a Survey[J]. IEEE Transactions on Automation Science and Engineering, 2016, 13(1):313-332.

- [12] XIA Yanjiang, HUPPE B S, FUKAMI T. An Approach to Enlarging the Maximum Bit in Piezoelectric Digital Actuator[J]. Ferroelectrics, 1994, 160(1):331-336.

- [13] XIAO Wenlei, HUAN Ji, LIU Guoxi, et al. A Digitally Linear Piezoelectric Bimorph Actuator in Open-loop Mode [J]. Applied Physics Letters, 2013, 102(12):123503.

- [14] 高强, 朱勇, 钱鹏飞, 等. 阵列压电叠堆驱动高速开关阀的设计与仿真分析[J]. 液压与气动, 2023, 47(9):56-62.

- GAO Qiang, ZHU Yong, QIAN Pengfei, et al. Design and Simulation Analysis of a High Speed-on/off Valve Actuated by Array Piezoelectric Stacks [J]. Chinese Hydraulics & Pneumatics, 2023, 47(9):56-62.

- [15] 崔玉国, 孙宝元, 董维杰, 等. 压电陶瓷执行器迟滞与非线性成因分析[J]. 光学精密工程, 2003, 11(3):270-275.

- CUI Yuguo, SUN Baoyuan, DONG Weijie, et al. Causes for Hysteresis and Nonlinearity of Piezoelectric Ceramic Actuators[J]. Optics and Precision Engineering, 2003, 11(3):270-275.

- [16] QI Chenkun, GAO Feng, LI Hanxiong, et al. An Incremental Hammerstein-like Modeling Approach for the Decoupled Creep, Vibration and Hysteresis Dynamics of Piezoelectric Actuator[J]. Nonlinear Dynamics, 2015, 82(4):2097-2118.

- [17] QIN Yanding, TIAN Yanling, ZHANG Dawei, et al. A Novel Direct Inverse Modeling Approach for Hysteresis Compensation of Piezoelectric Actuator in Feedforward Applications [J]. IEEE/ASME Transactions on Mechatronics, 2013, 18(3):981-989.

- [18] 赵天, 杨智春, 刘昊, 等. 压电陶瓷叠层作动器迟滞蠕变非线性自适应混合补偿控制方法[J]. 航空学报, 2018, 39(12):222308.

- ZHAO Tian, YANG Zhichun, LIU Hao, et al. Hysteresis and Creep Nonlinearities Modeling and Adaptive Hybrid Compensation Control of Piezoelectric Stack Actuators [J]. Acta Aeronautica et Astronautica Sinica, 2018, 39(12):222308.

- [19] TASHAKORI S, VAZIRI V, APHALE S S. A Comparative Quantification of Existing Creep Models for Piezoactuators[C]// Recent Trends in Wave Mechanics and Vibrations. Cham, 2023:419-426.

(编辑 陈勇)

**作者简介:**凌杰\*,男,1990年生,副教授、博士。研究方向为精密驱动与控制。E-mail:meejing@nuaa.edu.cn。

**本文引用格式:**

凌杰,张允执,陈龙,等.数字压电叠堆执行器:原理、建模与控制[J].中国机械工程,2025,36(2):228-237.

LING Jie, ZHANG Yunzhi, CHEN Long, et al. Digital Piezoelectric Stack Actuators: Principle, Modeling and Control[J]. China Mechanical Engineering, 2025, 36(2):228-237.

**(上接第 227 页)**

[20] 喻莹,徐新卓,罗尧治.基于Kresling折纸构型的空间结构可控失稳模式研究[J].工程力学,2021,38(8):75-84.

YU Ying, XU Xinzhuo, LUO Yaozhi. Programmable Instability of Spatial Structures Based on Kresling Origami [J]. Engineering Mechanics, 2021, 38(8):75-84.

(编辑 陈勇)

**作者简介:**徐齐平,男,1986年生,副教授。研究方向为软体致动器、软体机器人。E-mail:xuqiping@zjnu.edu.cn。鄂世举\*(通信作者),男,1970年生,教授、博士研究生导师。研究方向为软体致动器、介电弹性体发电机、智能材料与机器人。E-mail:esx\_2001@zjnu.edu.cn。

**本文引用格式:**

徐齐平,张柯航,张宏伟,等.真空驱动软体可折展致动器驱动特性研究[J].中国机械工程,2025,36(2):220-227.

XU Qiping, ZHANG Kehang, ZHANG Hongwei, et al. Study on Actuation Characteristics of Vacuum-driven Soft Deployable Actuators[J]. China Mechanical Engineering, 2025, 36(2):220-227.